The 5 Classic CPU Stages

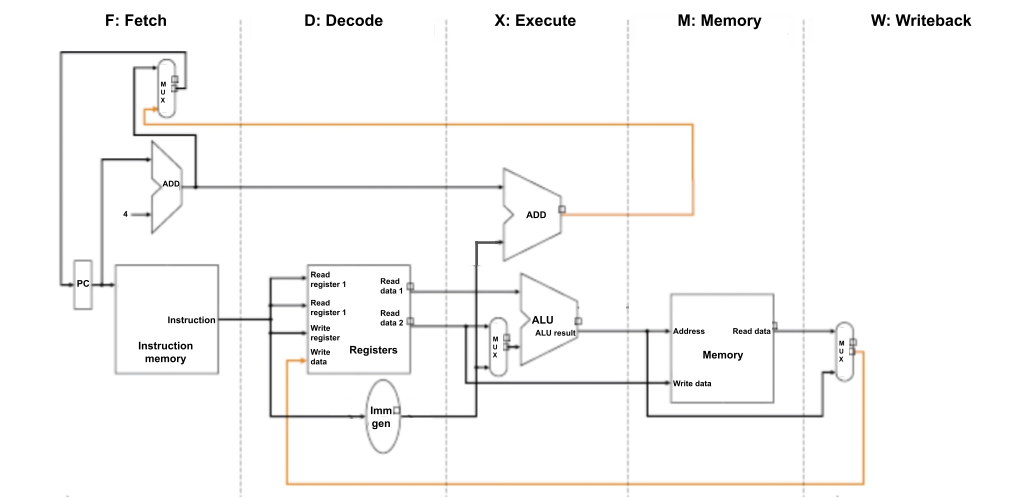

Consider the following diagram of our RISC-V processor datapath.

We can break down all the things that a CPU needs to do for every instruction into stages:

- Fetch the instruction from the instruction memory.

- Decode the instruction bits, producing control signals to orchestrate the rest of the processor. Read the operand values from the register file. For example, this stage needs to convert from a binary encoding of each register index into a “one-hot” signal to read from the appropriate register.

- EXecute the actual computation for the instruction, using the arithmetic logic unit (ALU): add the numbers, shift the values, whatever the instruction requires.

- Access Memory, reading or writing an address in the external data memory. Only some instructions need this stage—just loads and stores.

- Write results back into the register file. The result could come from the ALU or from memory, if it’s a load instruction.

As the bolding in this list implies, computer architects often abbreviate these stages with a single letter: F, D, X, M, or W.