## CS 316: Logic and State

Kavita Bala Fall 2007 Computer Science Cornell University

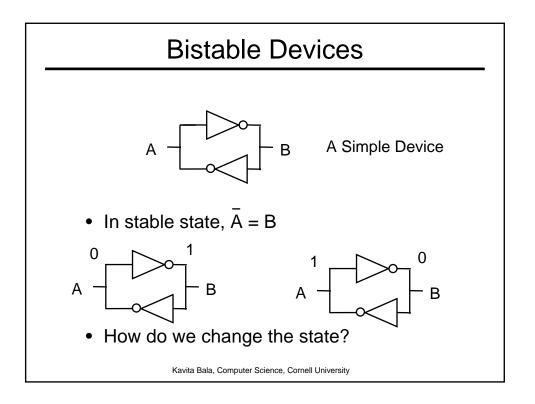

Stateful Components

- Until now is combinatorial logic

- Output is computed when inputs are present

- System has no internal state

- Nothing computed in the present can depend on what happened in the past!

- Need a way to record data

- Need a way to build stateful circuits

- Need a state-holding device

Kavita Bala, Computer Science, Cornell University

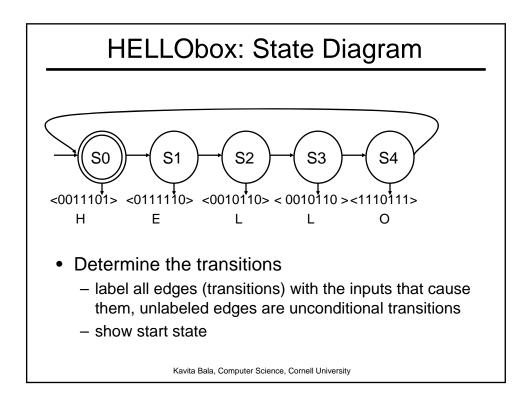

| HELLObox: State Table                                                                                     |                       |                |         |  |  |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------|----------------|---------|--|--|--|

| <ul> <li>Build state table         <ul> <li>rote encoding of<br/>the state diagram</li> </ul> </li> </ul> | Current<br>State      | Next<br>State  | Output  |  |  |  |

| J                                                                                                         | S0                    | State<br>S1    | 0011101 |  |  |  |

|                                                                                                           | S1                    | S2             | 0111110 |  |  |  |

|                                                                                                           | S2                    | S3             | 0010110 |  |  |  |

|                                                                                                           | S3                    | S4             | 0010110 |  |  |  |

|                                                                                                           | S4                    | S0             | 1110111 |  |  |  |

| Kavita Bala, C                                                                                            | omputer Science, Corr | ell University | 1       |  |  |  |

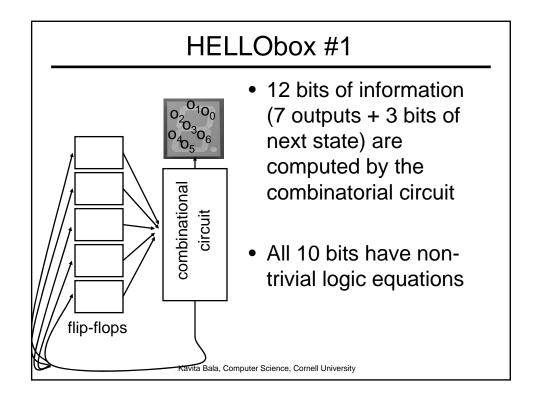

| HELLObox: State Assignment 1                                                         |                         |               |         |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------|---------------|---------|--|--|--|

| <ul> <li>Assign bit patterns to<br/>states</li> </ul>                                |                         |               |         |  |  |  |

| <ul> <li>Try to make resulting device simple</li> <li>One option is shown</li> </ul> | Current<br>State        | Next<br>State | Output  |  |  |  |

|                                                                                      | 000                     | 001           | 0011101 |  |  |  |

| Determine logic                                                                      | 001                     | 010           | 0111110 |  |  |  |

| equations for                                                                        | 010                     | 011           | 0010110 |  |  |  |

| <ul> <li>– every bit of output</li> <li>– next state</li> </ul>                      | 011                     | 100           | 0010110 |  |  |  |

| – for every flip-flop and                                                            | 100                     | 000           | 1110111 |  |  |  |

| Output Kavita Bala, Computer                                                         | Science, Cornell Univer | sity          |         |  |  |  |

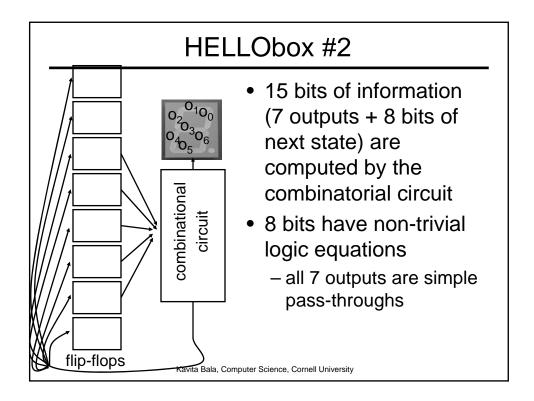

| HELLObox: State Assignment 2                                                                          |                  |               |         |  |  |  |

|-------------------------------------------------------------------------------------------------------|------------------|---------------|---------|--|--|--|

| <ul> <li>Assign bit<br/>patterns to<br/>states to make<br/>the resulting<br/>device simple</li> </ul> | Current<br>State | Next<br>State | Output  |  |  |  |

|                                                                                                       | 00111010         | 01111100      | 0011101 |  |  |  |

|                                                                                                       | 01111100         | 00101100      | 0111110 |  |  |  |

|                                                                                                       | 00101100         | 00101101      | 0010110 |  |  |  |

| • Here, we use                                                                                        | 00101101         | 11101110      | 0010110 |  |  |  |

| far more bits<br>than necessary                                                                       | 11101110         | 00111010      | 1110111 |  |  |  |

| – to simplify the                                                                                     |                  |               |         |  |  |  |

| combinatorial                                                                                         |                  |               |         |  |  |  |

| Circuit<br>Kavita Bala, Computer Science, Cornell University                                          |                  |               |         |  |  |  |

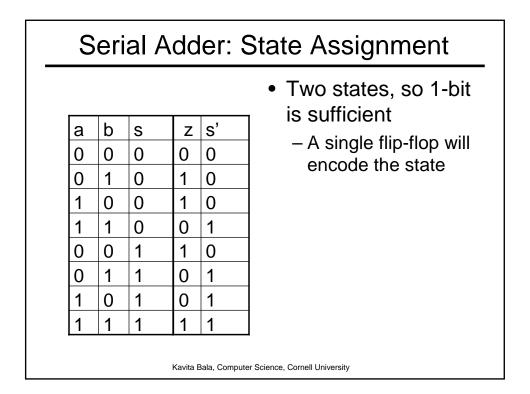

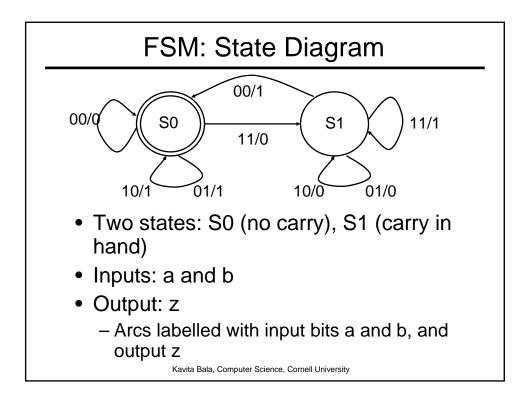

|   | Serial Adder: State Table                         |       |   |               |                                                        |  |  |

|---|---------------------------------------------------|-------|---|---------------|--------------------------------------------------------|--|--|

| а | b                                                 | state | z | next<br>state | <ul> <li>Write down all input<br/>and state</li> </ul> |  |  |

| 0 | 0                                                 | S0    | 0 | S0            | combinations                                           |  |  |

| 0 | 1                                                 | S0    | 1 | S0            |                                                        |  |  |

| 1 | 0                                                 | S0    | 1 | S0            |                                                        |  |  |

| 1 | 1                                                 | S0    | 0 | S1            |                                                        |  |  |

| 0 | 0                                                 | S1    | 1 | S0            |                                                        |  |  |

| 0 | 1                                                 | S1    | 0 | S1            |                                                        |  |  |

| 1 | 0                                                 | S1    | 0 | S1            |                                                        |  |  |

| 1 | 1                                                 | S1    | 1 | S1            |                                                        |  |  |

|   | Kavita Bala, Computer Science, Cornell University |       |   |               |                                                        |  |  |